IonMonkey/Overview

Jump to navigation

Jump to search

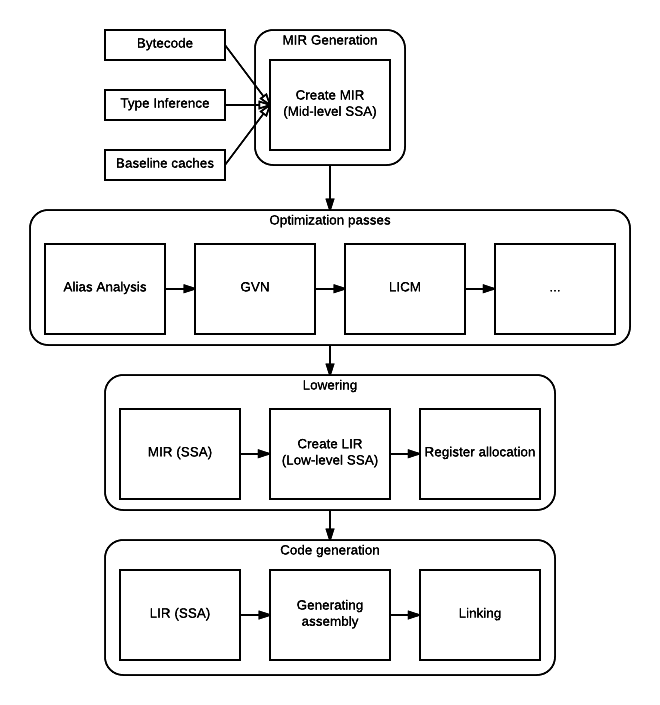

IonMonkey compilation occurs in four major overall phases:

- MIR Generation. This phase transforms SpiderMonkey's bytecode into a control-flow graph and an architecture-independent, SSA-form IR.

- Optimization. The MIR analyzed and optimized. This is where global value numbering (GVN) and loop-invariant code motion (LICM) occur.

- Lowering. The MIR is transformed into an architecture-specific IR (still in SSA form) called LIR. Register allocation occurs on LIR.

- Code generation. The LIR is transformed into native assembly for x86, x64, or ARM (or what have you).

The full pipeline is roughly outlined with the following diagram:

Each major phase of the pipeline is separated into four articles:

Lastly, if you're interested in porting IonMonkey to a new CPU architecture, you might want to take a look at IonMonkey/Porting.